概要

本書ではオリジナルのCPUをゼロから設計することで,CPUの内部構造を理解するとともに,CPU設計の面白さを読者に伝えていきたいと考えています。

本書はCPUの設計をメインターゲットとしていますが,CPUだけでなく周辺機器を制御するためのI/Oやバスの設計を行い,SoCとしました。CPUだけでなく,ボードの設計やソフトウェアの設計までコンピュータに必要な要素を全てをカバーします。ハードウェアからソフトウェアまで全てを自分でゼロから設計・実装し,実機で動かします。CPUの設計から基板の設計,そしてソフトウェアの設計までを1冊の書籍で扱うことで,それぞれの関連性を包括的に理解することを可能にしています。

本書は大きく3つの章から構成されています。第1章ではCPUを中心に,プログラムやデータを格納するためのメモリや,外部との入出力を行うためのI/O,それらを繋ぐバスを作成し,簡単なコンピュータシステムを作成します。第2章では,このコンピュータシステムを実機で動作させるための基板を設計・製作します。第3章では,このコンピュータシステム用のプログラミングを行い,実機にて動作確認を行います。本書の最大の特徴は,コンピュータシステムをすべて自作可能ということです。

3つの章はそれぞれ独立しており,読者の興味に応じて好きな章のみを選択して読むことができます。

こんな方におすすめ

- エンジニアを目指している学生

- オリジナルアーキテクチャのCPUを設計・実装したい方

- オリジナルFPGA基板を設計・製作したい方

- アセンブラでのプログラミングをしたい方

追加情報

リファレンスボードの購入先

本書で設計・製作するものと同様のデザインのFPGA基板を,下記のWebショップから購入することができます。

サポート

ダウンロード

ダウンロードについて

以下の「ダウンロード」より,ファイル名をクリックしてください。

ご注意ください

ダウンロードされたファイルについて,万一障害が発生し,その結果いかなる損害が生じたとしても,小社および著者は責任を負いかねます。必ずご自身の判断と責任においてご利用ください。

再配布ついて

ダウンロードしたオリジナルのファイル,それらを改編したもの,ともに再配布する場合は無保証であることと,著作者を明記したうえでの再配布を可能といたします。なお,商用利用は不可とさせていただきます。

以上のことをご確認,ご了承の上,データをご利用願います。

- 【第1章】

- 仕様書:AZPR_datasheet_1.01.pdf

- RTL:AZPR_RTL.zip

- モジュール階層表

- ファイル階層表

※2012年10月23日付けで,【第1章】の仕様書を差し替えました。それ以前にダウンロードされた方は,お手数ですが再度ダウンロードしていただきますよう,お願いいたします。

- 【第2章】

- FPGA基板のEagleデータ:AZPR_FPGA.zip

- 電源基板のEagleデータ:AZPR_POW.zip

- AZPR EvBoardの部品ライブラリ:lib.zip

- Eagleファイルの使用方法

- FPGA基板の3D表示:AZPR_3D.zip(2012年11月28日付けで追加)

- 【第3章】

- ソースコード:Sample_Program.zip

- アセンブラ:azprasm.zip

- UrJTAGの設定ファイル:UrJTAG_Setting.zip

- ダイアグプログラムのbit, mcs, svfファイル:AZRP_EvBoard_Diag.zip

- 制約ファイル:AZPR_EvBoard.ucf(2013年5月15日付けで追加)

- 【お試し版PDFファイル】

- お試し版PDFファイル:978-4-7741-5381-0-otamesiban.pdf(2017年11月27日付けで追加)

正誤表

本書の以下の部分に誤りがありました。ここに訂正するとともに,ご迷惑をおかけしたことを深くお詫び申し上げます。

(2013年9月2日更新)

P.30 2~3行目

| 誤 |

「8進数では0から8で数値を表現します。」 |

|---|

| 正 |

「8進数では0から7で数値を表現します。」 |

|---|

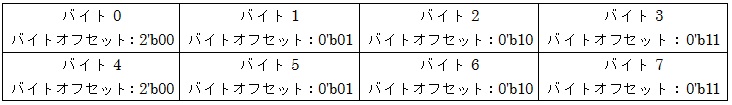

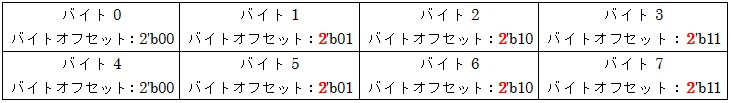

P.46 図1-38の【例】

P.84 図1-76の【アドレスとメモリの対応】

※クリックすると,画像を大きく表示できます。

P.112 上から3行目

| 誤 |

MEMステージで実行さるため、 |

|---|

| 正 |

MEMステージで実行するため、 |

|---|

P.403 上から8行目

| 誤 |

「AZPR_EvBoartd.ucf」 |

|---|

| 正 |

「AZPR_EvBoard.ucf」 |

|---|

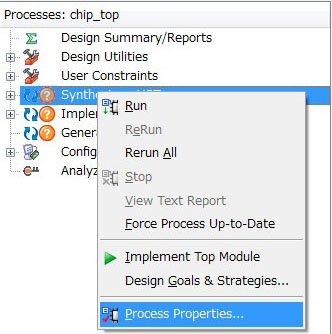

P.403 合成オプションについて

ISEの論理合成時に面積重視のオプションを選択する必要がありましたが,必要な記載が漏れておりました。

「ISE Project Navigator」ウィンドウの左下にある「Synthesize」を右クリックし,「Process Properties」を選択します。

「Process Properties」ダイアログの「-opt_mode」の値を「Area」に変更してください。

その後は書籍の手順通り進めてください。

書籍の手順に沿ってFPGAにXC3S250Eを使用してAZPR EvBoardを製作された場合には,上記の手順が必要です。

なお,市販されているAZPR EvBoardに搭載されているFPGAはXC3S500Eで,充分な論理ブロックがあるため,上記の手順は不要です。

P.451 表3-10 ASCIIコード表

10進の「41」,「64」,「97」が飛んでおり,10進と16進,文字の対応がずれてしまっております。

修正した表を掲載いたしますので,こちらをご参照ください。

補足情報

ソフトのバージョンアップによる齟齬をきたした部分

(2013年3月21日更新)

P.76

- Icarus Verilogによるコンパイルコマンド

最新版のIcarus Verilogでは、オプションを最初に記述して、ソースコードとテストベンチは最後に指定する必要があります。

※本書に記載されているバージョン(ver.0.9.5)ではこの問題は起きません。

iverilog -s regfile_test -o regfile_test.out regfile_test.v regfile.v

|