目次

第1章 プロセッサとコンピュータシステムの基礎

1.1コンピュータの構造

- コンピュータの構成要素 ― プロセッサ,メモリ,入出力装置

- Column プロセッサパッケージの物理的な構造

- コンピュータは2進法で計算を行う

- プロセッサ ― プログラムを解釈するコンピュータの頭脳

- Column 2値と多値 ― 必ず2進法,ではない!?

- プロセッサの命令の実行 ― ベルトコンベア式の流れ作業

- Column プロセッサ,マイクロプロセッサの定義 ― コンピュータの最重要部品としてのプロセッサ

- サイクルタイム,クロック周波数

- Column パイプラインの段数

- CPUという呼称

- プロセッサ現在 ― 用途の広がり

- Column 倍率を表す接頭語

- 命令アーキテクチャとマイクロアーキテクチャ ― ソフトウェア的な構造とハードウェア的な構造

- メモリ ― コンピュータの「命令」と「データ」を記憶する

- メモリ容量 ― どれだけの情報を記憶できるか

- その「K」は210か,103か

- バイト(B) ― 8ビット単位で情報を扱う

- アドレス

- メモリレイテンシ

- DIMM ― コンピュータの部品としてのメモリ

- バス ― プロセッサ,メモリ,入出力装置をつなぐ

- データ転送速度とメモリ

- 入出力装置 ― コンピュータの目,耳,口

- 入出力装置は種類が多い ― 基本/高速/各種用途向けの入出力装置

- I/Oバス ― PCI Express規格

- プロセッサと入出力装置の関係

- ノースブリッジとサウスブリッジ ― 薄れつつある呼称

1.2 コンピュータの高速化を支える半導体技術

- ムーアの法則 ― より多くのトランジスタ。並列度を高める方向へ

- デナードスケーリング ― トランジスタの性能を向上

- 膨大な開発投資が支える半導体の微細化 ― 微細化のペースは今後しばらくは継続

- 性能向上の三本柱 ― クロック向上,並列処理と,機能拡張

1.3 コンピュータとデータの表現

- バイト,ハーフワード,ワード... ― ビットのグループと用途

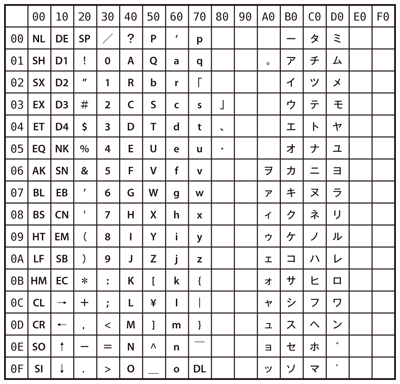

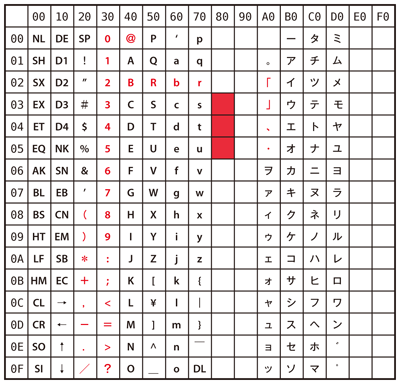

- 文字コード

- 符号無し整数と符号付き整数,1の補数表現と2の補数表現

- Column 日本語と文字コード

- 浮動小数点数 ― IEEE 754規格

- ビッグエンディアンとリトルエンディアン

- ビッグエンディアンか? リトルエンディアンか?

1.4 プロセッサと命令

- 命令アーキテクチャ入門

- Intel x86アーキテクチャの命令形式

- x86という呼称について

- 機械命令 ― プロセッサへの命令

- アドレス空間

- 32ビットアドレス空間

- 64ビットアドレス空間 ― AMD86-64,Intel 64

1.5 機械命令プログラムの作り方

- アセンブラによるプログラミング

- Column AMDとIntelの64ビット拡張アーキテクチャ

- コンパイラを使う高級言語によるプログラミング

- 最適化

- インタプリタによるプログラミング

- JITコンパイル

1.6 まとめ

- Column 半導体の微細化

第2章 プロセッサの変遷

2.1 コンピュータ以前の計算装置

- そろばん ― 計算をするための最初の道具

- ネイピアの骨 ― 掛け算の補助具

- 機械式計算機 ― Schikardの計算機,Pascaline

- BabbageのDifference Engine ― 歯車を使うスパコン

2.2 初期の電子式コンピュータ

- 最初の電子式コンピュータ ― ABCとENIAC

- FUJIC ― 日本初の電子式コンピュータ

2.3 プロセッサを構成する素子の変遷

- 主要な部品に基づくコンピュータの世代分類

- 第1世代:真空管

- 第2世代:トランジスタ

- TRANSARC S-2000

- 第3世代:集積回路(IC,LSI)

- 第4世代:大規模集積回路(VLSI)

- Intel 4004

- MOSFETと性能向上,CMOS

- Intel 4004(1971年) vs. 2010年現在のマイクロプロセッサ

- VLSIプロセッサの素子数,クロック周波数のトレンド

2.4 命令アーキテクチャの変遷

- 命令アーキテクチャ発展の道

- プログラム内蔵式コンピュータ ― プログラムもメモリから読み込む

- 仮想記憶 ― もっと潤沢に。メモリをたっぷり使いたい

- 仮想記憶のしくみ

- マルチプロセス ― プログラムの配置替えが必要

- TSSと,メモリ管理機構の登場

- メモリ管理機構,特権状態 ― マルチユーザではセキュリティ問題を解決する必要がある

- ページ方式とセグメント方式

- 特権状態とユーザ状態

- Column MULTICS,その後

- ISA拡張 ― 命令アーキテクチャの確立と,命令互換性の実現

2.5 マイクロアーキテクチャの発展

- マイクロアーキテクチャ発展の道

- パイプライン処理 ― パイプラインレジスタを用いて,ハードウェアを有効利用する

- パイプライン処理実現の難所 ― 素子数の増加に伴いパイプライン処理が普及してきた

- 演算器の高速化 ― 整数演算器,浮動小数点演算器

- 整数演算器 ― 加減算はとくに重要である

- 浮動小数点演算器

- キャッシュ ― 「メモリアクセス」問題に対処する秘密の小箱

- キャッシュの魔法

- RISCの出現 ― RISCとCISC

- RISCの特徴,CISCの特徴

- RISC方式のプロセッサとCISC方式のプロセッサ

- スーパースカラ実行 ― 複数の命令を1サイクルに実行する

- Out-of-Order実行 ― 命令の順序を変更して性能を上げる

- 20~30%程度の性能向上が見込めるOut-of-Order実行

- 分岐予測と投機実行 ― 「条件分岐命令」対策

- Column 「Out of Order」にご注意(!?)

- マルチコア ― 消費電力の制約がマルチコア化をプッシュ

- ハードウェア量と性能の関係 ― グロシュの法則の今

- 消費電力の増加とマルチコア化

2.6 用途が広がるプロセッサ

- さまざまな舞台で活躍するプロセッサ

- 省電力,高信頼技術,リアルタイム性 ― さまざまな要件

2.7 まとめ

第3章 [詳説]プログラマのためのプロセッサアーキテクチャ

3.1 マイクロアーキテクチャを支える技術

- パイプライン実行のしくみ ― 「並列」に命令を処理する

- 命令の実行とハードウェア構造

- パイプラインの動き

- 構造的ハザード ― 「プロセッサの資源を取り合う」問題

- データハザード ― 「前の仕事が終わらないと次に進めない」問題

- 制御ハザード ― 「条件分岐命令」問題

- キャッシュのしくみ ― メモリアクセスを加速する

- キャッシュラインとタグ ― データの塊と,中身を示す小さなデータ

- メモリとキャッシュ間のデータ転送はキャッシュライン単位

- フルアソシアティブ方式のキャッシュ ― 自由度が高い

- ダイレクトマップ方式のキャッシュ ― 構造が簡単

- セットアソシアティブ方式 ― 良いとこ取りの中間的な方式

- キャッシュによる性能改善効果

- プロセッサの記憶階層

- キャッシュをうまく使うプログラミング

- RISCとCISC ― 固定長命令と可変長命令

- 命令のデコードが難しい ― CISC命令と問題[1]

- パイプライン実行が難しい ― CISC命令と問題[2]

- 互換性を維持して内部をRISC化 ― x86のCISC命令を,RISC風の内部命令に変換してから実行する

- ロード,ユースの引き離し ― RISCの特徴[1]

- RISCはCISCより多くの命令メモリが必要 ― RISCの特徴[2]

- 演算器の高速化 ― プロセッサ中で処理が複雑で時間のかかる部分の一つ

- 整数加算器の高速化

- 整数乗算器の高速化

- 除算の高速化 ― SRT除算アルゴリズム

- 浮動小数点演算器とその使い方

- スーパースカラ実行のしくみ ― 1サイクルに複数の命令を並列実行する

- 1サイクルに複数命令を実行するために

- Out-of-Order実行のしくみ ― データハザードの影響を軽減する

- リザベーションステーション

- 逆依存性の問題

- リネーム ― 逆依存性を解消

- 正確な割り込みを保証

- メモリバリア命令/FENCE命令 ― メモリアクセスの順序が変わると問題になる場合がある

- 分岐予測のしくみ ― 制御ハザードによる損失を低減する

- ループの振る舞い(おさらい)

- 分岐予測 ― 分岐方向の予測と予測実行

- 飽和カウンタを使う予測 ― Taken,Not Takenの履歴を使う

- 履歴を用いる分岐予測 ― ローカル履歴

- その他の分岐予測機構 ― グローバル履歴,Gshare,ハイブリッド分岐予測

- 現代のプロセッサは各種ハザードを解消,軽減して性能を上げている

- メモリ,I/Oと入出力インタフェース

- コモンバス ― 伝統的なインタフェース

- 入出力の制御

- パフォーマンスカウンタ ― プロファイラ,プロセッサ内部の実行状況の情報

- パフォーマンスカウンタの構造

3.2 プロセッサの利用範囲を広げるアーキテクチャ拡張

- マルチプログラミングとメモリ管理機構

- メモリのフラグメンテーション ― セグメント方式が抱える問題

- ページ方式 ― 現在主流のメモリ管理

- 多階層のアドレス変換

- メモリを効率的に利用したい ― TLBミスの軽減,ページサイズ,ラージページ

- 割り込み処理機構

- ポーリング

- Column 例外,割り込み,トラップ ― 用語の整理

- 割り込みのしくみ

- トラップ ― プロセッサ内部の異常を知らせる

- ベクタ割り込みと割り込みレベル

- 仮想化のサポート ― メモリアクセスとメモリ管理機構

- VMM,仮想化

- VMM,OS,メモリ管理機構

- マルチメディア,暗号などのサポート ― 大量データを扱う計算処理

- SIMD演算器 ― マルチメディア処理,並列演算

- 暗号化処理

3.3 x86 Nehalemアーキテクチャのプロセッサ

- x86の命令体系,Intel 64アーキテクチャについて

- IA-32e モード ― Compatibility,64ビット

- x86のレジスタセット

- x86で扱えるデータタイプ

- x86プロセッサの命令形式

- Core i7プロセッサの構成

- 命令を取り出して解釈する「フロントエンド」

- 各種処理を行う「実行エンジン」

- Nehalemの「キャッシュ階層」

- メモリ管理は4階層のテーブルを使用

- 4階層ページテーブル

- ページの使い方を決めるページ属性

- 新しいプロセッサインタフェースQPI

3.4 まとめ

第4章 仮想化サポート

4.1仮想化の目的,メリット/デメリット

- 仮想化の基礎知識(おさらい)

- 仮想化の目的

- 強固なユーザ間分離を実現する ― 仮想化のメリット[1]

- 複数サーバをまとめて稼働率を改善する ― 仮想化のメリット[2]

- VMMの実行オーバヘッド ― 仮想化のデメリット,注意点

- 大量のメモリが必要

- 資源の割り当て管理が必要 ― Webホスティングサービスの例

4.2 仮想化を実現するために

- OSに独立の(仮想)ハードウェアを提供するVMM

- メモリの仮想化

- ゲストOSのハードウェアアクセスをインターセプトする

4.3 仮想化をサポートするハードウェア機構

- ハードウェア操作命令の検出

- 特権違反例外処理

- ハードウェア状態の退避,復元 ― 仮想マシンの切り換え

- 仮想マシン制御情報

- 二重のアドレス変換,TLB

- シャドウページテーブル ― x86のハードウェアテーブルウォーク機構

- 仮想TLB方式 ― もう少し上手なシャドウテーブルの作り方

- EPT,NPT ― 二重のアドレス変換を自動化するハードウェア機構

- I/Oの仮想化

- 正統的なI/O仮想化 ― VMMがI/Oをエミュレーション

- パススルー方式 ― 入出力装置を1つの仮想マシンに割り当てる

- Para Virtualization(準仮想化)方式 ― ハイレベルI/O要求を使う

- ライブマイグレーション

4.4 まとめ

- Column 仮想化の始まり

第5章 マルチプロセッサの出現と普及

5.1 マルチスレッドプロセッサ

- スレッド,マルチスレッドの氾濫(!?) ― まずは用語のおさらいから

- マルチスレッドの二つの方式

- VMT(垂直マルチスレッド) ― 複数のスレッドを切り替えて実行する

- SMT(同時マルチスレッド) ― 複数のスレッドの命令を混ぜて実行する

- VMTのしくみ ― 短時間でスレッドを切り替える

- VMTに必要なメカニズム

- SMTのしくみ ― 複数のスレッドの命令を混ぜる

- Column 実は長い歴史のあるSMT

- SMTに必要なメカニズム

- マルチスレッドの効果はいかに? ― Windowsタスクマネージャに見る例

- スレッド間の資源競合 ― 性能向上への影響

- マルチスレッド化による性能向上効果 ― スループット性能は10~30%程度向上

- チップ面積とスループット性能向上のバランス

5.2 マルチプロセッサシステム

- マルチプロセッサ,マルチコアとは何か?

- マルチコアプロセッサの構造

- Column メニーコアプロセッサの構造

- キャッシュコヒーレンシ制御 ― マルチプロセッサのキャッシュ間の整合性

- MSIプロトコル

- MESIプロトコル

- MOSIプロトコルとMOESIプロトコル

- マルチソケットシステム

- インクルージョンキャッシュ

- ノンインクルージョンキャッシュ

- キャッシュコヒーレンシとスケーラビリティ

- Column ソケット? チップ?

- プロセッサチップ間接続インタコネクトとメモリ ― HyperTransport,QPI

- Column マルチコア時代の,プロセッサ,CPUの意味するところ

- マルチプロセッサシステムの性能向上 ― 問題と対策

- 資源競合 ― 3次キャッシュ,メモリインタフェース

- キャッシュラインのフォールスシェアリング

- アムダールの法則とロードインバランス

- 発熱がクロックを制限

- 共有メモリシステムと分散メモリシステム

- メモリ空間とキャッシュ間のコヒーレンシ

- 分散メモリシステムの使い勝手

- 共有メモリ,分散メモリのハードウェアコスト

- クラスタシステム

5.3 まとめ

第6章 プロセッサ周辺技術

6.1 メインメモリ技術

- メインメモリの歴史のおさらい

- ダイナミックメモリ

- SRAM,DRAM

- メモリの性能向上 ― 70年で140万倍の容量アップ,5000万倍のスピードアップ

- DRAMメモリの動作原理 ― 電荷で情報を記憶する

- DRAM記憶セルへの書き出し

- DRAM記憶セルからの読み出し

- リフレッシュ ― DRAM,SRAMの由来

- DRAMチップとメモリDIMM

- DIMMのさまざまな種別

- DRAMチップの内部構造 ― セルアレイ,行/列デコーダ,センスアップ,バンク

- ページ,バースト長

- プロセッサとDIMMの接続

- メモリとのデータ転送,メモリアクセス

- メモリシステムのエラー対策

- パリティチェック ― メモリのエラーを見つける

- ECC ― メモリのエラーを訂正する

6.2 入出力装置の接続

- プロセッサのI/O接続

- PCIバス

- PCIバスとPCI Express

- Column PCIバス登場までの道のり

- PCIバスの制御構造

- PCIの階層構造とバス番号,バスブリッジ

- IntelのCore iシリーズプロセッサのI/O構造

- Intel PCHのI/O制御構造

6.3 まとめ

- Column DRAMのリフレッシュ

第7章 GPGPUと超並列処理

7.1 GPGPUのしくみ

- 3DグラフィックスとGPU ― 大量の計算が必要

- GPU

- GPUシステム

- GPUからGPGPUへ

- 「超並列SIMDプロセッサ」としてのGPGPU

- AMD HD 5870 GPU

- NVIDIA Fermi GPU

- 「超マルチスレッドプロセッサ」としてのGPGPU

- GPGPUのメモリ階層

- (1次)キャッシュ部分 ― GPGPUとキャッシュコヒーレンシ

- Column ワープ!

- GPUは高速のGDDR DRAMを使う

- AMD HD 5870 GPUのメモリ階層

- GPGPUプログラミングではデータをどのメモリに置くか明示する

- GPGPUのマルチスレッドは汎用レジスタを分割使用する

- CPUとGPGPUの大きな違い

- 超並列SIMD処理による強力な演算能力

- 巨大マルチスレッドプロセッサ,同じ命令列の実行

- メモリ空間の使い分け

7.2 GPGPUプログラミング

- GPGPUプログラミングの今

- CUDAの実行モデル ― スレッドブロック,グリッド

- CUDAでの関数の宣言,変数の宣言

- OpenCLのプログラミング

- GPGPUの性能を引き出すには

- データ転送やプログラム起動のオーバヘッドを減らす

- ワープ内の全スレッドを有効に動かすことが重要 ― 並列化アルゴリズムを作る

- 演算あたりのメモリアクセスを減らすタイリング

- ダブルバッファリング ― データ転送と演算をオーバラップさせる

- メモリアクセスのバンクコンフリクトを減らす

- 同期回数を減らす

7.3 まとめ

- Column Top500とGPUコンピューティング

第8章 今後のプロセッサはどうなっていくのか?

8.1 消費電力がすべてを支配する

- なぜプロセッサは電力を消費するのか

- 漏れ電流の増加

- デナードスケーリングの頭打ちと,続くムーアの法則による性能向上

- 省電力技術の発展

- DVFS

- ターボブースト,ターボコア

- 省電力マイクロアーキテクチャの採用 ― クロックゲート,キャッシュ機構...

- 現代のさまざまなプロセッサと消費電力対策

8.2 より高性能へ,より多くの機能を

- 半導体の微細化技術

- 増加するトランジスタをうまく使うには?

- 二つのアプローチ ― マルチコア化,周辺機能の取り込み

- 一部のトランジスタをコストダウンに使う

- 良品率,不良品率

- 一部のブロックが不良のチップを有効利用する

- Intel Xeon 5600シリーズ

- PS3のCELLプロセッサ,Fermi GPU

8.3 より高信頼で安全なプロセッサ設計

- なぜプロセッサは誤動作するのか ― 故障,ノイズ

- 中性子,アルファ線によるノイズ

- トランジスタの傷みが引き起こす誤動作

- 誤動作を防いで安全に動かす

8.4 今後のプロセッサの方向性とは?

- さまざまなシステムで使われるプロセッサ

- 家電用プロセッサ

- 自動車用プロセッサ

- PC用プロセッサ

- スマートフォン用プロセッサ

- サーバ用プロセッサ