目次

第1章 FPGAの内部といろいろなFPGAボード

1-1 FPGAとは

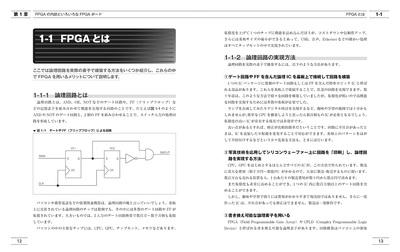

- 1-1-1 論理回路とは

- 1-1-2 論理回路の実現方法

- 1-1-3 HDLによる論理回路の表現

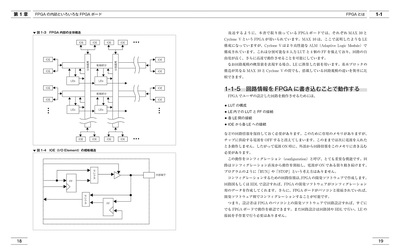

- 1-1-4 FPGA内部の基本構造

- 1-1-5 回路情報をFPGAに書き込むことで動作する

- 1-1-6 本書で用いたFPGAの規模

- 1-1-7 内蔵メモリの構成

1-2 各種FPGAボードの紹介

- 1-2-1 入手しやすくなったFPGAボード

- 1-2-2 かつては雑誌の付録にもなったFPGAボード

- 1-2-3 学習に適したFPGAボードの条件

- 1-2-4 FPGAボードの比較

1-3 回路情報のダウンロード

- 1-3-1 コンフィグレーション方法

- 1-3-2 USB-Blasterは多機能だけど高価

1-4 第1章のまとめ

コラムA Altera FPGAからIntel FPGAへ

第2章 FPGAの回路設計を体験

2-1 開発ソフトウェアQuartus Prime

- 2-1-1 Quartus Primeとは

- 2-1-2 FPGAの開発手順

- 2-1-3 開発ソフトウェアや設計データのダウンロード

2-2 回路設計とコンパイル

- 2-2-1 7セグメントデコーダの設計

- 2-2-2 プロジェクトの作成

- 2-2-3 ピンアサイン

- 2-2-4 コンパイル

- 2-2-5 コンパイルエラーの対策

2-3 コンフィグレーションと回路の拡張

- 2-3-1 FPGAボードの準備

- 2-3-2 コンフィグレーションの実施

- 2-3-3 1秒桁への拡張

- 2-3-4 1秒桁回路のコンパイルと動作確認

2-4 第2章のまとめ

- 2-4-1 まとめ

- 2-4-2 課題

コラムB 各操作の目的とアウトプットを意識して操作しよう

第3章 もう少し進んだ回路設計

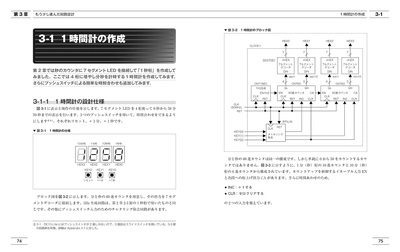

3-1 1時間計の作成

- 3-1-1 1時間計の設計仕様

- 3-1-2 ブロックごとにモジュールを分けた回路記述

- 3-1-3 プロジェクトを作成して動作確認

3-2 状態遷移を回路で実現

- 3-2-1 時刻合わせ機能の仕様

- 3-2-2 ステートマシンの回路構造

3-3 時刻合わせ機能付き時計の設計

- 3-3-1 全体ブロックと各カウンタの作成

- 3-3-2 修正桁点滅の実現

- 3-3-3 制御部と最上位階層を作成

- 3-3-4 コンパイルし動作を確認

- 3-3-5 実用的な拡張案

3-4 第3章のまとめ

- 3-1-1 まとめ

- 3-4-2 課題

第4章 波形観測による回路デバッグ

4-1 ロジックアナライザとは

- 4-1-1 デバッグの基本は波形観測

- 4-1-2 ロジックアナライザの基本動作

- 4-1-3 FPGAの中にロジックアナライザを組み込む

4-2 SignalTap IIを組み込んで波形観測

- 4-2-1 SignalTap IIの組み込み

- 4-2-2 SignalTap IIによる波形観測

4-3 第4章のまとめ

- 4-3-1 まとめ

コラムC FPGAは本当に高性能なのか?

第5章 FPGA内蔵CPUを試す

5-1 Nios IIプロセッサとは

- 5-1-1 FPGA にCPUを内蔵させるメリット

- 5-1-2 ソフトマクロとハードマクロ

- 5-1-3 Nios IIプロセッサの概要と種類

- 5-1-4 数多く用意されている周辺回路

5-2 Nios IIシステムの構築

- 5-2-1 Nios IIに7セグメントLEDとスイッチを接続

- 5-2-2 Qsysでシステムを構築

- 5-2-3 最上位階層の作成とコンパイル

5-3 プログラムの作成と実行

- 5-3-1 プログラムの作成

- 5-3-2 Nios II EDSによるビルド

- 5-3-3 回路のコンフィグレーションとプログラムのダウンロード

- 5-3-4 プログラムの実行

5-4 第5章のまとめ

- 5-4-1 まとめ

- 5-4-2 課題

第6章 自作周辺回路の接続とAPIの利用

6-1 Nios IIのバス

- 6-1-1 バスとはなにか

- 6-1-2 Nios IIシステムのバス「Avalonバス」

- 6-1-3 Avalon バスの主要信号とタイミング

- 6-1-4 バス幅の違いを吸収するスイッチ・ファブリック

6-2 自作周辺回路の設計と接続

- 6-2-1 自作PIOに7セグメントLEDとスイッチを接続

- 6-2-2 自作周辺回路をQsysに組み込む

- 6-2-3 制御プログラムの作成と実行

6-3 タイマー割り込みによるAPI活用例

- 6-3-1 作成システムの仕様とタイマーブロックの構造

- 6-3-2 タイマー内蔵のNios IIシステムを構築

- 6-3-3 ポーリングによるプログラム例

- 6-3-4 割り込みを使ったプログラム例

- 6-3-5 HAL APIを使ったプログラム例

6-4 第6章のまとめ

- 6-4-1 まとめ

- 6-4-2 課題

コラムD プログラムをダウンロードできない!?

第7章 いろいろな周辺回路を設計

7-1 キーボードとマウス接続回路

- 7-1-1 PS/2インターフェースの仕様概要

- 7-1-2 PS/2インターフェース回路の設計

- 7-1-3 Nios IIシステムへの組み込み

- 7-1-4 キーボードのテストプログラム

- 7-1-5 サンプリングクロックを工夫して波形観測

- 7-1-6 マウスのテストプログラム

- 7-1-7 スクロールホイールへの対応

7-2 VGA文字表示回路

- 7-2-1 VGAインターフェースの仕様概要

- 7-2-2 VGA文字表示回路の設計仕様

- 7-2-3 ブロック図とタイミングチャート

- 7-2-4 IP Catalogによるメモリの生成

- 7-2-5 Qsys階層の作成とシステムの完成

- 7-2-6 Nios II EDSにより動作確認

7-3 第7章のまとめ

- 7-3-1 まとめ

- 7-3-2 課題

第8章 外部メモリを用いたグラフィック表示回路

8-1 外部SDRAMの制御

- 8-1-1 SDRAMの概略

- 8-1-2 SDRAMのテストシステムを構築

- 8-1-3 SDRAMコントローラとPLLの接続

- 8-1-4 SDRAMテストプログラムによる動作確認

8-2 グラフィック表示回路の作成

- 8-2-1 Avalon-MMのマスター

- 8-2-2 グラフィック表示回路の仕様

- 8-2-3 グラフィック表示回路の構成と回路記述

- 8-2-4 FIFOの作成

- 8-2-5 グラフィック表示回路システムの構築

- 8-2-6 リンカスクリプトを修正してビルドし動作確認

コラムE 画像ファイルの表示

8-3 第8章のまとめ

- 8-3-1 第8章のまとめ

- 8-3-2 課題

第9章 CMOSカメラの接続と応用

9-1 カメラモジュールの概要と接続

- 9-1-1 CMOSカメラモジュールの概略

- 9-1-2 OV7725の画像系タイミング

- 9-1-3 SCCB仕様と主要レジスタ

- 9-1-4 カメラモジュールの接続

9-2 キャプチャ回路

- 9-2-1 キャプチャ回路システムの概略

- 9-2-2 キャプチャ回路の詳細

9-3 SCCBコントローラの作成とシステムの構築

- 9-3-1 SCCBの詳細タイミング

- 9-3-2 SCCBコントローラの構成

- 9-3-3 システムの構築とテストプログラムの作成

9-4 動画録画機能の実現

- 9-4-1 動画記録と再生の仕組み

- 9-4-2 動画記録再生のプログラム

9-5 第9章のまとめ

- 9-5-1 第9章のまとめ

- 9-5-2 課題

コラムF 制約ファイルの読み方書き方

Appendix I 開発環境の構築

I-1 開発ソフトウェアのダウンロードとインストール

- I-1-1 Quartus Primeのダウンロード

- I-1-2 Quartus Primeのインストール

I-2 USB-Blasterドライバのインストール

Appendix II 各FPGAボード利用上の注意点

II-1 DE10-Lite

- II-1-1 3個目のプッシュスイッチの代わりにスライドスイッチを割り当て

- II-1-2 PS/2コネクタをArduino 端子に接続

- II-1-3 内蔵メモリを使う際の設定

- II-1-4 PLLが異なる

II-2 DE1-SoC

- II-2-1 コンフィグレーションでは一手間必要

- II-2-2 画像用のD/Aコンバータを搭載

- II-2-3 ARMコアを内蔵したSoC FPGAチップを搭載

II-3 設計データの利用方法

- II-3-1 設計データの内容

- II-3-2 設計データ利用上の注意点

- II-3-3 Quartus Primeを立ち上げずに動作を確認する方法

- II-3-4 Quartus Primeでプロジェクトを作成して動作を確認する方法

Appendix III 回路データおよびプログラムのROM化

III-1 各FPGAボードごとのROM化方法

- III-1-1 DE0-CV

- III-1-2 DE10-Lite

- III-1-3 DE1-SoC

III-2 Nios IIプログラムのROM化

- 参考文献

- 索引