Flash Moduleと接続ケーブル

取材では取り出したFlash Moduleを見せてもらいました。外側はアルミで覆われており、

Andy:外側はヒートシンクになっています。全体に並列にアクセスするために熱くなるんです。Flash自体はローパワーなのですが、

ミリオン単位のIOPSを受けるとフラッシュチップとコントローラのチップを合わせて、 50Wになるんです。 筆者:うお……

(50W×36モジュールで1. 8KWにもなります) Andy:性能のためです。もしI/

Oがなければほとんどゼロなんですが。つまりハイパフォーマンスがこれだけのパワーを持っていくのです。D5 1つで最大3,000W。通常動作時はこの半分と思えば良いでしょう。タダでハイ・ パフォーマンス、 というのは存在しないんだよ (ははは) 筆者:まあ3KWでもいいでしょう。HPCの世界ではそういったことが起きていますし、

最近のアプリケーションは徐々にHPCに近づいていますからね。 Andy:そのとおり。多くのHPC

(企業) や政府がそう考えていると思います。ともかくこれが業界で初めてのdual portでhot swap可能なNVMeモジュールです。バッテリはなく、 スーパーキャパシタが入っており、 これで書き込み途中に電源喪失があってもデータを最後まで書けます。現在D5には4TバイトのFlash Moduleが用意されていますが、 次の18ヵ月で倍に上げていきます。 このFlash ModuleはDSSD専用のものですが、

HBAとケーブルもやはりDSSD製です。HBAはPCIeブリッジチップが1つ載っているだけで、 それほど特別なものではないと思われますが、 筆者が驚いたのはむしろそのケーブルです。持ってみるとPCIe gen3 4 laneを通すとは思えないほど細くしなやかで、 見るからに小さなそのコネクタにパッと見て数えるのが困難なほど細かなピッチでピン接点が並んでいます。 筆者:このケーブルですが……

Andy:ケーブルは特別製です

(Andyは質問の途中で答える傾向がある。負けずに質問を続けなければなりません)。 筆者:とても細いですね。距離について気にしているんですが。

Andy:接続できるのは1ラックです。光ファイバについて探しています。それで30mかそれ以上まで届きますが、

しかし今は (銅線のケーブルで) とにかく1ラック距離です。 筆者:なるほど。ちょっと気にしていました。というのもユーザは大きなサーバを使いたかったりします

(1ラックに入るサーバの数は限られている)。 Andy:そう、

だから2ラック目にも (なんとか) 届く。つまり左右隣のラックにサーバを置いてそこに届くようにすることはできます。

写真の上端にHX-2と書かれているのがHBAカードです。P1、

Multicast RDMA

ディスクアレイで利用されているRAIDなど、

が、

さて、

筆者:私の理解ですが、

Multicast RDMAってのは業界で初めてではないですか? Andy:そのとおりです。シリコン

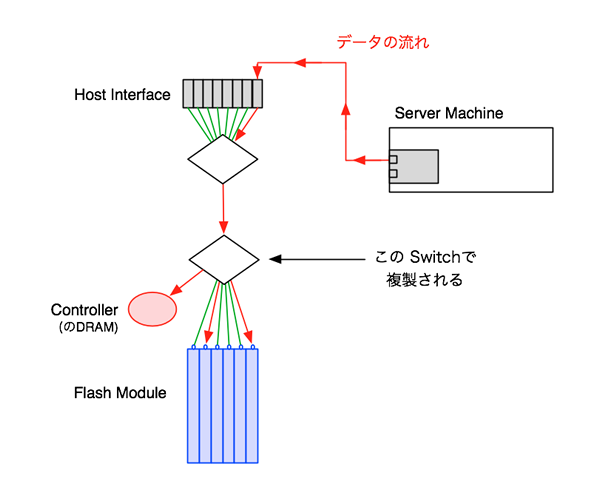

(FabricのPCIeスイッチチップ) には (以前から) 導入されていたのですが、 今まで誰も使ったことがなかったのです。まず、 データを書き込むと、 1つはコントローラのDRAMに書かれ、 それ以外にもコピーが2つFlash Moduleに作られます。しかし我々は複数回の転送を行いません。データをPCIe Fabricに入れて、 これらのコピーを並列にFlashに書きます。

この説明で、

筆者:OK、

ただ私はスイッチレイヤでのオーバーサブスクリプションが気になるのです。 Andy:いや、

これ (Multicasting) はLower Layerで行われます [3]。 筆者:どこですか?

Andy:Flash Module に直接つながれているところ

(図2参照) です。ここで複製されるのであって、 上の PCIe Switch では行われません。

なるほどこの位置での複製であれば、

D5の設計上の工夫は、

なお、

取材でもCubic RAIDのCheck-sum領域の計算と書き込みは事後

スタートアップストーリー

AndyはDSSDに起業のときから関わっています。やたらに技術的なことばかり聞いてきたので、

筆者:スタートアップの経緯を聞かせてください。

Andy:2010年にOracleがSun Microsystemsを買収しました。このときDSSDの創業者であるBill Mooreが、

他に4人のソフトウェアエンジニアと一緒にSunを離れました。とても革新的な製品を作るためにね。我々はこのPCIeとNVMeを完全にミックスする企業を立ち上げたのです。当時NVMeはまだよく定義されていませんでしたが、 そのパフォーマンスのポテンシャルがとても高かったからです。 そこでの興味深い技術的チャンレジは、

ハードウェアがアプリケーションにパフォーマンスを届ける、 ということでした。デバイスとデバイスドライバ間のビットレベルのコーディングといったレベルからやるのです。いまどき、 たとえば、 GoogleとかSNSの会社などではそういうことをする人はそう多くないんですけどね。でもSunのエンジニアたちには性能を出すためにならデバイスドライバやデバイスハッキングをするのが好きな人がいるんですよ (笑) Jeff Bonwick、

Bill Mooreと、 Sunから来た何人かのキーエンジニアはSunのZFSファイルシステムやSolarisでのI/ O処理のこと、 つまり通常のシステムにおける入出力処理スタックのことをとてもよく理解しています。そこから得た結論は、 つまりこれに最もフィットするのはI/ Oスタックをバイパスすることだ、 ということでした。 ところで我々は結局シリコン、

つまりチップの設計をしませんでした。というのも、 2010年に始めたとしても動き出すのは2013年になってしまって、 とても時間が掛かります。そのときに必要となるパフォーマンスの予測がとても難しいのです。 筆者:そのデザインで最も技術的に困難だったところは何ですか?

Andy:多くのイシュー

(解決すべき事項) がありました。というのも、 すべてをスクラッチでやりましたからね。だから次のバージョンは比較的早くできあがると思います。もしあなたが初めて、 まったく新しいアーキテクチャをやるとなったら、 あなたは考えられる限りのありとあらゆる問題に当たらなければならないんですよ。 それでも最大のイシューはパフォーマンスでした。我々はハードウェアそのものがパフォーマンスを出せることはわかっていたんです。つまりロックなしのマルチスレッドのI/

Oシステムの実装がパフォーマンスをアプリケーションまで届けることが鍵でしたが、 そのようなソフトウェアを誰も作っていなかったのです。トータルでのパフォーマンスを得るために、 我々のシステムは潜在的には1,000とか10,000のパラレルストリームがこの箱に同時に流れ込むようなことができるものです。 筆者:PCIeによるスイッチファブリック自体は開発したのですか?

Andy:そこもシリコンについては動くものがありました。すべてのチップは新しい製品ですが、

とにかくそれまで誰一人として、 このサイズでのファブリックを作れた者はいなかったのです。そのためにすべてのアーキテクチャはスクラッチから作りました。きつい仕事 (heavy lifting) でしたね (ははははは) 筆者:何人くらいでスタートしたのですか?

Andy:初期は20~30人でした。すぐ50人になって、

いま250人ほどです。これはまあEMCからの大きな投資があってこそなんですが。 筆者:主たるアイディアや目的はあなたから出たものですか?

Andy:いや、

私からではありません。クリアにしておきましょう。ファウンダは他のソフトウェアアーキテクチャの人たちです。私が関わったのはハードウェアコンセプトと、 ハードウェア設計そのものです。 また、

私は将来使えるようになるシリコン (チップ群) のことをよく知っていました [6] からね。ともかく私が寄与したのはすべてハードウェアに関することです。すべてのソフトウェアについては、 Bill Moore、 Jeff BonwickとMike Shapiroなど他の人たちによって行われました。 ともかく私はこの技術にとても興味がありました。というのは、

これがとても広い技術範囲をカバーしていたからです。そして当初とても不可能に思えた大規模な並列処理を実現しました。これが最高のパフォーマンスを得る方法なのです。

本稿でこれまで説明したように、

そうした工夫はまだまだあります。たとえば、

Andy:いま誰でもNVMeのPCIe Flash Cardを買うことができますが、

それらはサーバにローカルに接続されます。するともしサーバが故障したらデータにアクセスできなくなります。そこで我々はこのインターフェースをFabricに取り出して、 サーバがもはやFlashを持たないようにしました。その結果、 Flashメモリはバーチャルなプールになります。そうすることで (そこに高い並列度でアクセスすることが可能になり)、 高い性能が得らるようになりました。

つまり、

筆者は長くコンピュータシステムを見ていますが、