お詫びと訂正(正誤表)

本書の以下の部分に誤りがありました。ここに訂正するとともに、ご迷惑をおかけしたことを深くお詫び申し上げます。

(2025年12月16日最終更新)

P.160の下から9行目

| 誤 |

その後の裏面研削で溝に達したとき、点でチップを |

|---|

| 正 |

その後の裏面研削で溝に達した時点でチップを |

|---|

P.170の項見出し

| 誤 |

ダイボンディング工程が不要 |

|---|

| 正 |

ワイヤボンディング工程が不要 |

|---|

P.191「寸法を計測」の図

| 誤 |

|

|---|

| 正 |

|

|---|

P.60の下から13行目

| 誤 |

134nm(193nm ÷ 1.44 = 1.34nm) |

|---|

| 正 |

134nm(193nm ÷ 1.44 = 134nm) |

|---|

P.34 下から5行目

| 誤 |

領域をウェルといい、pウェルはnMOS領域にp型 |

|---|

| 正 |

領域をウェルといい、pウェルの形成ではnMOS領域にp型 |

|---|

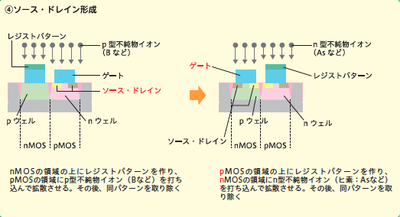

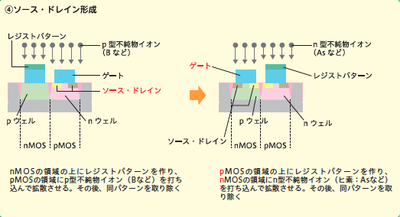

P.37の図④ソース・ドレイン形成(左側)

P.37の図④ソース・ドレイン形成(左側)

| 誤 |

nMOSの領域の上にレジストパターンを作り、pMOSの領域にn型不純物イオン(ヒ素:Asなど)を打ち込んで~ |

|---|

| 正 |

pMOSの領域の上にレジストパターンを作り、nMOSの領域にn型不純物イオン(ヒ素:Asなど)を打ち込んで~ |

|---|

P.37

図④ |

|

|---|

P.123の表

| 誤 |

超高真空の環境下で材料を加熱蒸発させ、槓子された基板結晶上に |

|---|

| 正 |

超高真空の環境下で材料を加熱蒸発させ、加熱された基板結晶上に |

|---|

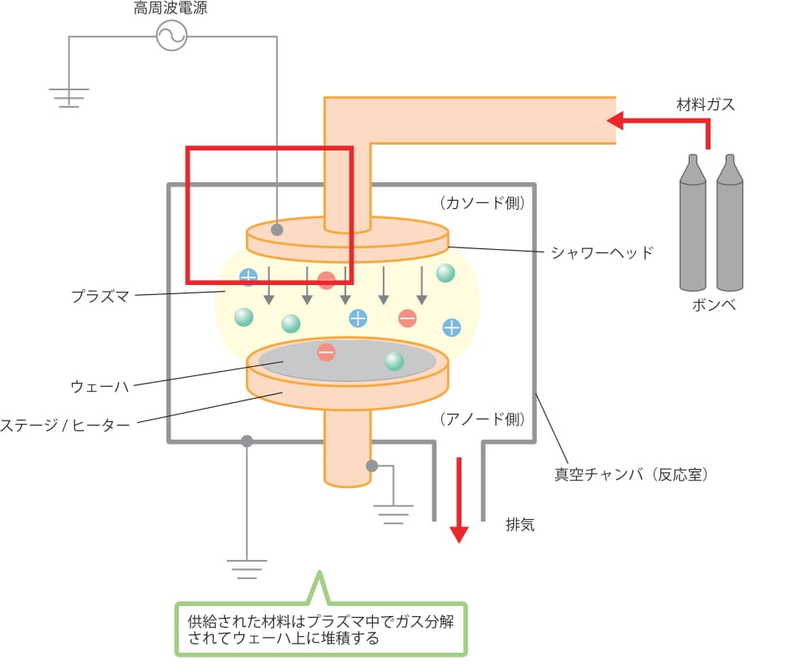

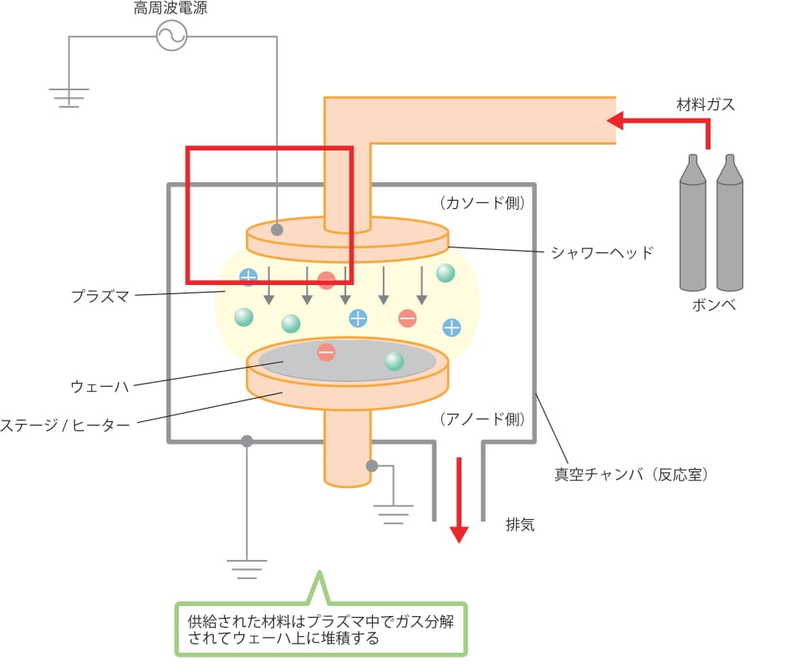

P.123の図

高周波電源は、カソード側のシャワーヘッドのあたりに接続される(赤い囲みの部分)。

| 正 |

|

|---|

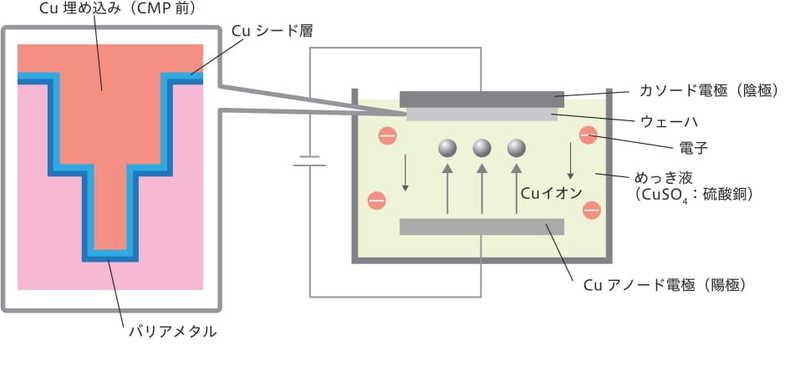

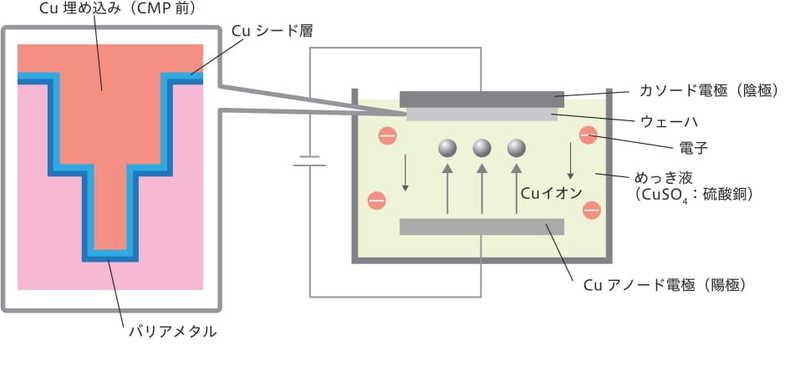

P.127の図

「電解めっきの原理」の図の電源記号の向きが逆になってしまっている。

| 正 |

|

|---|

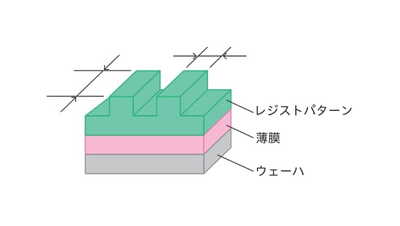

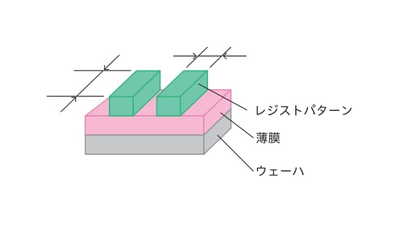

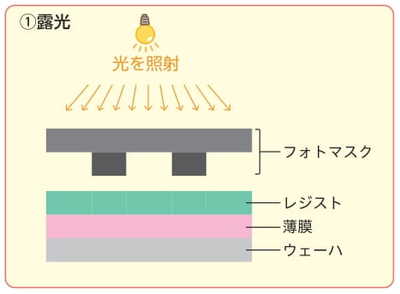

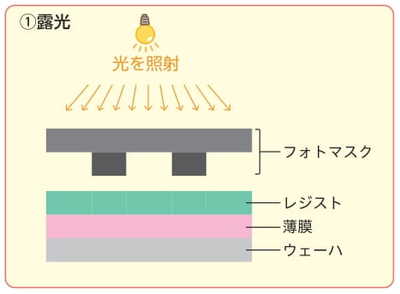

P.75の図

①露光の「フォトマスク」の部分が誤り。

| 正 |

|

|---|

P.63の「ダブルパターニング(SADP)」の図の⑤と⑥(2箇所)

P.109の「枚葉式」の図

P.109の「枚葉式」の図

P.135の「枚葉式クラスタシステムの例」の図

P.173の「電解めっき法のよるバンプ形成」の図

P.110の下から8行目